# RF Network-On-Chip (RFNoC™) Specification

Version 1.0.3

### RF Network-On-Chip (RFNoC™) Specification

Copyright © 2018-2021 Ettus Research, A National Instruments Brand

#### **About this Guide**

This guide describes RFNoC, which is a heterogeneous processing framework used to implement high throughput DSP in the FPGA for Software Defined Radio (SDR) systems in an easy-to-use and flexible way.

#### **Intended Audience**

This guide is written for hardware and software engineers who want to become familiar with the RF Network-on-Chip (RFNoC™) architecture or want to develop intellectual property (IP) using the RFNoC™ architecture.

#### **Release Information**

The following changes have been made to this specification:

| Version | Date       | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0.1     | 2/1/2019   | First Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 0.2     | 5/6/2019   | <ul> <li>Updated CHDR format to add virtual channel number and remove user defined flags and 2 bits of metadata</li> <li>Dropped redundant "ctrlport" signal name in Table 18</li> <li>Updated management NodeInfo response value</li> <li>Renamed AXIS Raw Data to AXIS Payload Context</li> </ul>                                                                                                                                                                                                     |  |

| 0.3     | 7/23/2019  | Added motherboard controllers     Added default properties                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 0.4     | 8/6/2019   | <ul> <li>Added description of RFNoC block user interface reset behavior</li> <li>Added "AXI-Stream Data" interface option to the Data-Plane</li> <li>Updated port numbering for user interfaces (eliminated "m_" and "s<q>_" in favor of concatenating multiple ports)</q></li> </ul>                                                                                                                                                                                                                   |  |

| 0.5     | 9/4/2019   | - Update interfaces from Doxygen                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 0.6     | 11/20/2019 | - Made various corrections and clarifications                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 0.7     | 8/28/2020  | <ul> <li>Updated document title to make it consistent throughout</li> <li>Updated copyright year</li> <li>Added clarification about Initialize stream command behavior based on NumBytes/NumPkts field values</li> <li>Added information on SIDEBAND_AT_END parameter</li> <li>Added YAML names to NoC Shell generation options</li> </ul>                                                                                                                                                              |  |

| 1.0     | 10/1/2020  | - Changed version from number to string in YAML                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 1.0.1   | 10/26/2021 | <ul> <li>Added explanation of the maximum amount of metadata that is compatible with all CHDR bus widths</li> <li>Corrected errors where stream status and route setup packets were mentioned instead of management packets</li> <li>Updated OpPayload description in the management packet field definitions table</li> <li>Deleted statement saying that management word padding is assumed to be zero and added clearer wording</li> <li>Added section "Data Item and Component Ordering"</li> </ul> |  |

| 1.0.2   | 5/18/2022  | Updated YAML example port names and types for timekeeper     Added description of ExtendedInfo for Node Info Response                                                                                                                                                                                                                                                                                                                                                                                   |  |

|       |          | <ul> <li>Added footnote about the sequence number for data packets, with or without timestamps.</li> <li>Clarified the meaning of tlength.</li> </ul> |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0.3 | 7/4/2025 | <ul> <li>Fixed minor spelling errors in AXI-Stream Data interface<br/>description.</li> <li>Updated Company Logos.</li> </ul>                         |

## **TABLE OF CONTENTS**

| 1 | INTR | ODUCT   | TION                                   | 6  |

|---|------|---------|----------------------------------------|----|

|   | 1.1  | What    | is RF Network-on-Chip (RFNoC™)?        | 6  |

|   | 1.2  | RFNo    | oC Basics                              | 6  |

|   |      | 1.2.1   | Components                             | 6  |

|   |      | 1.2.2   | Topology                               | 6  |

|   |      | 1.2.3   | Routing                                | 7  |

|   |      | 1.2.4   | Flow                                   | 7  |

|   | 1.3  | The R   | RFNoC Flow Graph                       | 8  |

|   |      | 1.3.1   | NoC Block                              | 8  |

|   |      | 1.3.2   | Stream Endpoint                        | 8  |

|   |      | 1.3.3   | Transport Adapter                      | 9  |

|   |      | 1.3.4   | Routing Core                           | 9  |

|   |      | 1.3.5   | Example Topology                       | 10 |

|   |      | 1.3.6   | Workflow                               | 10 |

| 2 | RFN  | OC FPG  | SA FRAMEWORK OVERVIEW                  | 12 |

| _ | 2.1  |         | S                                      |    |

|   |      | 2.1.1   | Block Capabilities                     | 12 |

|   |      | 2.1.2   | Integration with USRP Hardware         |    |

|   | 2.2  | RFNo    | oC Packet Network                      |    |

|   |      | 2.2.1   | CHDR Overview                          | 13 |

|   |      | 2.2.2   | Data Packets                           | 17 |

|   |      | 2.2.3   | Control Packets                        | 18 |

|   |      | 2.2.4   | Stream Status Packets [Internal Only]  | 22 |

|   |      | 2.2.5   | Stream Command Packets [Internal Only] |    |

|   |      | 2.2.6   | Management Packets [Internal Only]     |    |

|   | 2.3  | NoC E   | Block User Interface                   |    |

|   |      | 2.3.1   | Basic Signals                          | 29 |

|   |      | 2.3.2   | Control-Plane                          | 30 |

|   |      | 2.3.3   | Data-Plane                             | 36 |

|   |      | 2.3.4   | IO Ports (Advanced)                    | 46 |

|   |      | 2.3.5   | Backend RFNoC Interface                | 47 |

|   | 2.4  | RFNo    | oC FPGA Image                          | 48 |

|   |      | 2.4.1   | Workflow                               | 49 |

|   |      | 2.4.2   | Design Assembly Toolflow               | 49 |

|   |      | 2.4.3   | Initialization and Usage               |    |

| 3 | DENI | ԴԸ ഉഹട  | TWARE FRAMEWORK OVERVIEW               |    |

| 3 | 3.1  |         | S                                      |    |

|   | J. 1 | שמאטוני | J                                      |    |

|   | 3.2 Block Controller |                                |    |  |  |

|---|----------------------|--------------------------------|----|--|--|

|   |                      | 3.2.1 Block IDs                | 52 |  |  |

|   |                      | 3.2.2 Registers                | 55 |  |  |

|   |                      | 3.2.3 Block Properties         | 62 |  |  |

|   |                      | 3.2.4 Block Actions            | 64 |  |  |

|   |                      | 3.2.5 C++ API                  | 64 |  |  |

|   |                      | 3.2.6 Custom Block Controllers | 67 |  |  |

|   | 3.3                  | RFNoC Graph                    | 69 |  |  |

|   |                      | 3.3.1 Capabilities             | 69 |  |  |

|   |                      | 3.3.2 C++ API                  | 69 |  |  |

|   | 3.4                  | Streamers                      | 75 |  |  |

|   | 3.5                  | 3.5 Motherboard Controllers    |    |  |  |

|   | 3.6                  | uhd::multi_usrp API            | 78 |  |  |

| 4 | RFN                  | OC TOOLS OVERVIEW              | 80 |  |  |

|   | 4.1                  | Basics                         | 80 |  |  |

|   | 4.2                  | RFNoC ModTool                  | 81 |  |  |

|   |                      | 4.2.1 Overview                 | 81 |  |  |

|   |                      | 4.2.2 Input Format             | 82 |  |  |

|   | 4.3                  | RFNoC Image Builder            | 85 |  |  |

|   |                      | 4.3.1 Overview                 | 85 |  |  |

|   |                      | 4.3.2 Input Format             | 85 |  |  |

| 5 | INDE                 | <b>=</b> x                     | 87 |  |  |

|   | 5.1                  | Figures                        | 87 |  |  |

|   | 5.2                  | Tables                         | 87 |  |  |

## 1 Introduction

## 1.1 What is RF Network-on-Chip (RFNoC™)?

RFNoC is a heterogeneous processing framework that can be used to implement high throughput DSP in the FPGA, for Software Defined Radio (SDR) systems, in an easy-to-use and flexible way. RFNoC and GNU Radio can be used to implement heterogenous DSP systems that can span CPU-based hosts, embedded systems and FPGAs.

RFNoC can be used to implement DSP "flow-graphs" where DSP algorithms and IP blocks are represented as nodes in the graph and the data-flow between them as edges. RFNoC, which is a network-on-chip architecture, abstracts away the setup associated with the nodes and edges of the graph and provides seamless and consistent interfaces to implement IP in the FPGA and software.

### 1.2 RFNoC Basics

As a network-on-chip architecture, RFNoC employs the following design philosophies for its choice of topology, routing, flow and microarchitecture.

### 1.2.1 Components

RFNoC flow graphs have the following components:

- NoC Block: A core processing block that implements user-defined IP like DSP, radio communication, hardware communication, etc.

- Stream Endpoint: A block that serves at the starting point or termination point for a data or control stream.

- *Transport Adapter*: An abstraction for physical transports like Ethernet, USB, PCIe, etc. Transport adapters are typically specific to the hardware that RFNoC is running on.

- Routers: Modules that connect NoC Blocks, Stream Endpoints and Transport Adapters to allow the user to build a DSP flow-graph.

Each NoC block has two communication planes: 1) Data and 2) Control. The control plane is used for setup and configuration and is assumed to be a low-throughput transaction-based interface. The data plane is a high-throughput streaming interface for samples, bits, etc. It is possible to inject optional, high-throughput metadata into the data-plane.

### 1.2.2 Topology

The topology is defined as the set of connections between the various RFNoC components. The topology of an RFNoC network is completely user-defined, given that the network meets the bandwidth and resource requirements of the underlying hardware. RFNoC allows the user to connect their own DSP blocks to the available Ettus Research SDR-specific blocks in a flexible and arbitrary fashion to create any custom flow graph. RFNoC also provides the ability to

reconfigure the graph within certain user specified constraints. Reconfigurability can fall into the following categories:

- Run-time Reconfiguration: A part of the topology can be modified at runtime by changing software settings or physical connections between USRPs and FPGA accelerators. Runtime reconfiguration allows the software application to change the topology dynamically.

- Build-time Reconfiguration: A part of the topology is hard-coded into the FPGA image and requires an FPGA rebuild (or partial bitstream download using partial reconfiguration) to reconfigure.

- 3. *No Reconfiguration*: There are hard-coded connections, primarily due to hardware design decisions, that do not allow certain parts of the topology to be modified.

Run-time reconfiguration provides the most flexibility but has a higher implementation cost in terms of FPGA resources and upper limits on processing blocks. Build-time reconfiguration provides less flexibility but reduces some of the resource costs. RFNoC allows users to choose between build-time and run-time topology reconfiguration. Automated tools and scripts will allow users to make these tradeoffs in an easy-to-use way.

### 1.2.3 Routing

The routing backbone in RFNoC is responsible for moving data from block to block using a clearly defined strategy. RFNoC uses the following routing strategies for the control and data plane.

- Source Routing: A routing algorithm that chooses the entire path at the source. For source routing to be possible, the source must know every hop that a transaction will take and the local router port at each hop. This is different from, say, distributed or incremental routing, where the transit decision is taken locally at each router instead of globally.

- *Deterministic Routing*: If there are two paths from the source to the destination, then the source routing algorithm will pick the path deterministically.

- (Data Only) Circuit Switched: A circuit (a path between a source and destination) must be established and reserved when a stream between two ports on NoC blocks is active. When a circuit is reserved, the source port cannot talk to a different destination.

- (Control Only) Packet Switched: Any NoC block can send and receive control transactions from any other NoC block without restrictions. The source and destination are encoded in the packet.

### 1.2.4 Flow

The smallest unit of transfer in RFNoC is a packet or datagram, the Condensed Hierarchical Datagram for RFNoC (CHDR). Both data-plane and control-plane traffic is packetized in the CHDR format, and the packet-type is encoded within the packet. Data streams are always bidirectional. Within the FPGA, data flows in AMBA AXI4-Stream packets and uses the standard ready/valid flow control scheme (flit-buffer flow control). For lossy transports, the stream endpoint implements a high-level flow control scheme which is packet based (packet-buffer flow control).

## 1.3 The RFNoC Flow Graph

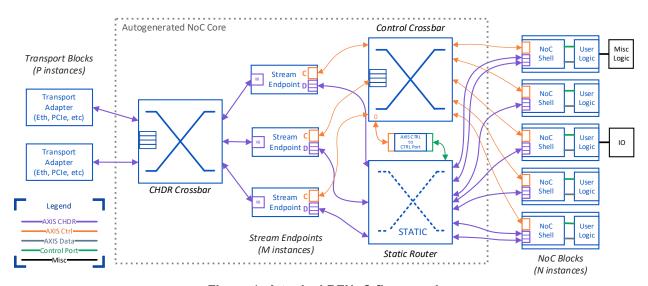

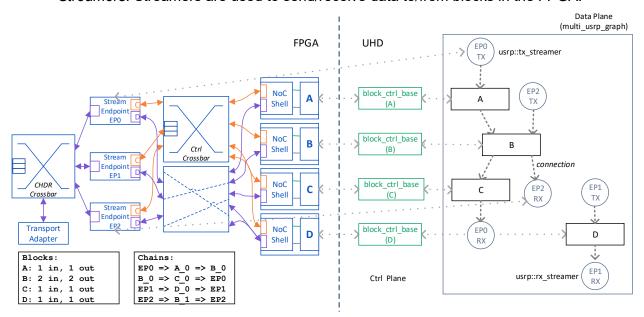

As shown in Figure 1 an RFNoC flow graph has the following major components

- NoC Blocks

- Stream Endpoints

- Transport Adapters

- Routing Core (Routers and Crossbars)

Figure 1: A typical RFNoC flow graph

### 1.3.1 NoC Block

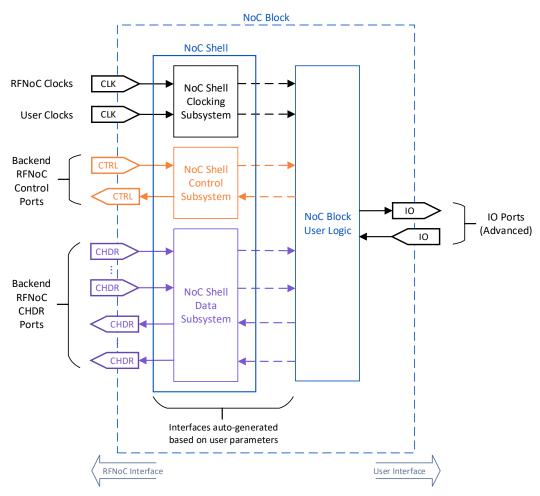

A NoC block contains the core processing IP (user logic) sandboxed from the rest of the blocks and from the framework. The user logic interacts with the RFNoC infrastructure using the NoC Shell module. The NoC shell provides a separate control and data interface that the user logic can use to send and receive control transactions and processing data, respectively. The details of each interface will be covered in later sections. A NoC block may also interface with outside logic or IO that is unmanaged by RFNoC. An RFNoC flow graph can have at most about 1000 NoC blocks per device (if they fit in the FPGA). This maximum number of ports in each FPGA is limited by a 10-bit address field which is shared for blocks, stream endpoints and transports.

### 1.3.2 Stream Endpoint

A stream endpoint serves as the start and end for a unique sample stream. The number of stream endpoints in a USRP design must scale with the number of parallel streams of data to/from the device. A stream endpoint can exist in the FPGA or in software. A bidirectional stream can be initiated between any two endpoints dynamically at any point in the application. Streams can be destroyed and recreated without having to rebuild or partially reconfigure the FPGA image. RFNoC implements flow control between stream endpoints, so they can flow over any transport. An RFNoC flow graph can have a user-selectable number of stream endpoints. The number of stream endpoints is independent of the number NoC blocks. The stream

endpoint can optionally support multiple virtual streams that are multiplexed through the same physical transport. The multiplexing and demultiplexing will be performed by the framework using the "virtual channel" field in the packet header.

### 1.3.3 Transport Adapter

A transport adapter is a wrapper around a specific transport implementation like Ethernet, Aurora, PCI Express, etc. Transport adapters provide logic to enable RFNoC-formatted dataflow between two FPGAs, or FPGA and software in a hardware-transparent way. The number of stream endpoints is independent of the number of transport adapters; a transport is capable of multiplexing multiple streams of data.

### 1.3.4 Routing Core

The routing core handles connecting NoC blocks, stream endpoints and transport adapters. The routing core has three main routers:

- CHDR Crossbar: This crossbar is a full-bandwidth full-mesh dynamic crossbar. It

connects the transport adapters to the stream endpoints. The CHDR crossbar enables

communication within an FPGA between any two of its crossbar ports. This allows

communication between two stream endpoints or between a stream endpoint and

another FPGA through a transport adapter.

- Control Crossbar: This crossbar is a local crossbar, also full-mesh, but with reduced bandwidth. It allows control transactions to be sent between any two of its ports. This allows control transactions to be sent from software to a NoC block, from a NoC block to software, between two NoC blocks, or from a NoC block to another FPGA.

- Static Router: The static router encodes a fixed topology between data ports of NoC blocks. This topology can only be reconfigured by rebuilding the FPGA image. A static router requires significantly fewer FPGA resources than a dynamic router.

### 1.3.5 Example Topology

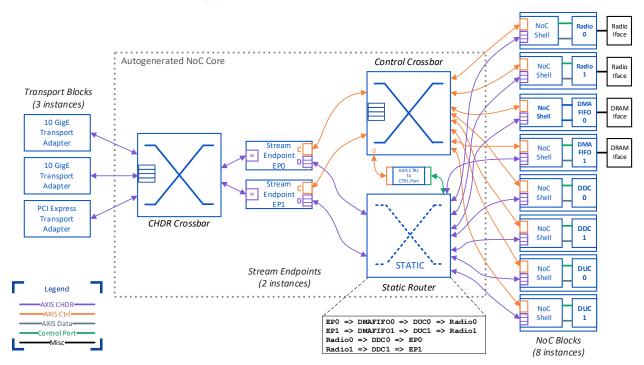

Figure 2: Example topology with for a multi usrp compatible image (X310 XG)

Figure 2 shows an example topology for the USRP-X310 that can function with the multi\_usrp API and a UBX daughter board (i.e., it has all the necessary radio and DSP blocks to implement the API). This design has:

- 3 transport adapters: 2 for 10 GigE and one for PCIe

- 2 stream endpoints: Each X310 supports 2 UBX daughter boards with a total 2 transmit and 2 receive channels. So, we instantiate 2 (bidirectional) stream endpoints.

- 8 NoC blocks: We have 2 each of the radio, DMA FIFO, DDC and DUC blocks. Together they form 4 chains (subgraphs). These chains hook up two of the 4 ports (TX and RX) of the stream endpoints.

- 2 crossbars: The 8 blocks in this image tunnel through 2 stream endpoints into the 5-port CHDR crossbar. The control crossbar has 11 ports for full control connectivity between blocks and endpoints.

### 1.3.6 Workflow

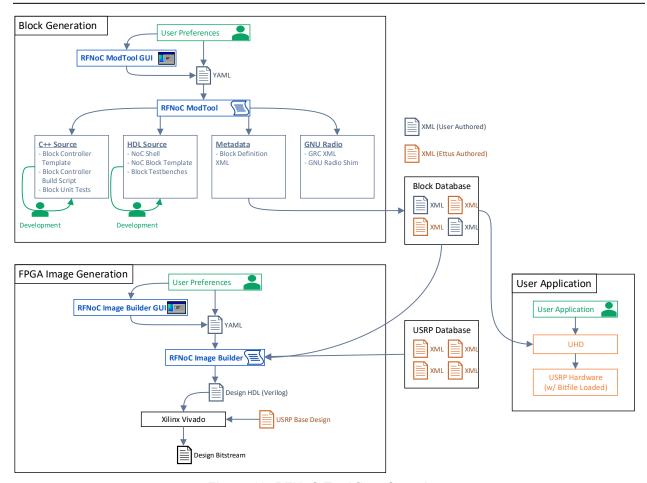

The primary goal for RFNoC is to allow DSP engineers to build heterogenous applications that may be comprised of standard blocks provided by Ettus Research, as well as custom user-authored blocks. The framework provides tools to 1) allow users to create custom blocks and 2) assemble an FPGA image and a software application that uses standard or custom blocks.

The general workflow for a user to build an RFNoC application thus is:

1. Partition the DSP/algorithm problem into software components and FPGA components (this can be done iteratively).

- 2. For the FPGA components, partition the problem into basic functions i.e. blocks.

- 3. Identify if any of the basic functions (blocks) are already available. Blocks can be found in the standard Ettus Research repositories or in third-party/open-source repositories.

- 4. Develop the FPGA and software source code for each new block using the tools provided by RFNoC.

- a. FPGA: Develop the core acceleration algorithm in Verilog, VHDL, SystemVerilog or Vivado HLS

- b. FPGA: Write testbenches for the block using the RFNoC framework

- c. Software: Write a block definition and an optional C++ controller to command and control the FPGA block from UHD software

- 5. Use the provided RFNoC tools to assemble an FPGA image that contains all the necessary blocks to implement the desired application.

- Connections between blocks can be fixed in the FPGA (for performance) or dynamic (for flexibility)

- Blocks can also be connected to transports on the USRP to build multi-FPGA applications

- 6. Once an FPGA image is ready, write an application in UHD (in C, C++ or Python) or GNU Radio to control and connect the dynamic blocks in the design to implement the desired application.

### Usage Guidelines

- The user develops individual blocks, so the user interface in the FPGA and software will be abstracted at a block level.

- Blocks have a control and data plane, and those planes will be the primary interface points in the software and the FPGA.

- To build an application, the user must compose blocks in a specified topology, so the framework will provide tools to do so on the FPGA and provide APIs in the software to build a graph of blocks.

- Device specific details and the board support package for a USRP will be abstracted away by the framework.

NOTE: RFNoC has several features that are marked as "advanced" that may be disabled or not exposed in the standard interfaces for performance or efficiency reasons. The advanced features will allow users to implement more complex applications but that may require detailed understanding of the framework.

## 2 RFNoC FPGA Framework Overview

### 2.1 Basics

### 2.1.1 Block Capabilities

Fundamentally, an RFNoC block has three main types of interfaces:

- Control: A transaction-based interface that can be used for low-speed control through software or other blocks. The three basic transaction types are register read, register write and bus sleep. More complex transactions are possible, but most applications should be possible with the basic three. All transactions on this interface can be deterministic and executed at user-specified times.

- Data: A streaming interface that can be used for high-speed and low-latency data movement between blocks. This interface also supports deterministic and timed streaming with optional (advanced) capabilities to insert inline metadata in the stream.

- External: A block may need access to other IO in addition to control and data. Blocks

that control USRP hardware (advanced) can have access to low-level pins. Blocks can

also get access to time to implement hardware timed operations. More advanced blocks

can get access to user-defined IO ports. Most RFNoC processing blocks will not need

the miscellaneous interfaces.

Each block has *one* bidirectional slave (or master and slave) control interface, *zero or more* data ports and *zero or more* external IO.

RFNoC is a network-on-chip and has a packetized transport network. Utilities are available to abstract packets into simple interfaces (discussed later), however the understanding of the data flow and packet formats should allow users to build better and more efficient applications. RFNoC provides the following capabilities for the control and data planes:

#### 2.1.1.1 Control-Plane Capabilities

- The control plane is transaction based. RFNoC has pre-defined transactions like reads, writes and sleeps, but it is possible to add more transactions (advanced). Transactions have a bit width of 32 bits and each transaction has a 20-bit address and a payload of up to eight 32-bit data words.

- Transactions are blocking and have an optional execution status.

- Transactions can be executed immediately or have an associated timestamp for deterministic execution or alignment with data samples.

- Any block can send transactions to any other block at any time. Blocks within an FPGA

have connectivity through a control crossbar, so other blocks can be addressed with a

10-bit "port" whereas blocks on remote FPGAs can be addressed through a stream

endpoint by specifying an "endpoint-ID" and a "port" on the remote FPGA.

### 2.1.1.2 Data-Plane Capabilities

- The data plane has a streaming interface where it is possible to stream "bursts" of

"vectors" of "items". An item is defined as a single atomic data word with a user-defined

bit-width (e.g., a common item would be an RF data sample). A vector is a 1dimensional collection of items. A burst is a collection of vectors.

- Data is received in packets which is independent of the items, vectors and bursts. The

parameters of a packet, like the size, are hardware dependent and can be used to make

low-level throughput/latency tradeoffs.

- Each packet can have user-defined metadata (advanced)

- Each packet can have a 64-bit timestamp (which is a counter in a time-base clock domain)

- It is possible to build a sequence of packets using an embedded sequence number field.

### 2.1.2 Integration with USRP Hardware

RFNoC provides seamless integration with USRP Hardware. As an SDR, a USRP has the following external input/output interfaces:

- ADCs/DACs

- RF Signal Chain Control

- Memory Interfaces (DDR, SRAM, etc.)

- Digital IO

- Transports (Ethernet, PCIe, etc.)

Each USRP will come equipped with NoC Blocks that seamlessly connect to the above IO. Transports will have corresponding transport adapters. It is possible to reassign that IO to other blocks in the design but that is an advanced feature.

### 2.2 RFNoC Packet Network

Before looking at the FPGA interfaces, it is important to understand how data flows between blocks and stream endpoints. With the provided RFNoC tools, it is possible to choose between a simple interface that abstracts the data movement or a low-level interface that gives the block full control (and responsibility).

### 2.2.1 CHDR Overview

The Condensed Hierarchical Datagram for RFNoC (CHDR) is a protocol that defines the fundamental unit of data transfer in an RFNoC network. As shown in Table 1, it has a header that encodes packet info, routing info, metadata and the data payload. CHDR is used as a transport protocol between stream endpoints. CHDR can handle control, data, flow control and status messages. The format is dependent on the width of the CHDR bus in the FPGA (CHDR W). NOTE: CHDR W can be a power of 2 that is equal to or greater than 64 bits.

| #     | Memory Layout<br><>    |     |     |         |             |         | Requir<br>ed? |         |   |

|-------|------------------------|-----|-----|---------|-------------|---------|---------------|---------|---|

| 0     | VC                     | EOB | EOV | PktType | NumMData    | SeqNum  | Length        | DstEPID | Υ |

|       | (6)                    | (1) | (1) | (3)     | (5)         | (16)    | (16)          | (16)    |   |

|       |                        |     |     |         | Value=M     |         | Value=L       |         |   |

| 1     | Timestamp (64)         |     |     |         |             |         | N             |         |   |

| 2     | Metadata[0] (CHDR_W)   |     |     |         |             |         | N             |         |   |

| •     | •••                    |     |     |         |             |         | •             |         |   |

| M+1   | Metadata[M-1] (CHDR_W) |     |     |         |             |         | N             |         |   |

| M+2   | Payload[0] (CHDR_W)    |     |     |         |             |         | Υ             |         |   |

| •     |                        |     |     |         |             |         | •             |         |   |

| M+N+1 |                        |     |     | Pay     | load[N-1] ( | CHDR_W) |               |         | N |

Table 1: Memory layout of a CHDR packet

The individual fields are described in detail in Table 2.

| Field                      | Width | Description                                                                                                                                                                                                                                                                                                                                                                              | Туре     |

|----------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Virtual<br>Channel<br>(VC) | 6     | The virtual channel number for a stream. It is possible to have multiple virtual streams flowing over the same physical stream (EPID-pair). This field identifies the index of the virtual stream. The default value of this field is zero.  NOTE: Any virtual streams that are incorrectly addressed will go to port 0.                                                                 | Required |

| Delimiters<br>(EOV/EOB)    | 2     | Delimiter flags for the user logic to use. These bits are unused by the core framework but have the following definitions:  • Delimiter[0] = EOV (End of Vector)  • Delimiter[1] = EOB (End of Burst)  NOTE: Data in RFNoC has three kinds of delimiters: 1)  Packets, 2) Vectors and 3) Bursts. A vector is a collection of packets (of items), and a burst is a collection of vectors. | Required |

| PktType                    |       |                                                                                                                                                                                                                                                                                                                                                                                          | Required |

|                                                                                                                               | 1  | Ov.4 - Combal Transportion                                                                                                                                                                                                                                                                                                                        |          |  |

|-------------------------------------------------------------------------------------------------------------------------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

|                                                                                                                               |    | 0x4 = Control Transaction                                                                                                                                                                                                                                                                                                                         |          |  |

|                                                                                                                               |    | 0x5 = <reserved></reserved>                                                                                                                                                                                                                                                                                                                       |          |  |

|                                                                                                                               |    | 0x6 = Data Packet without a Timestamp                                                                                                                                                                                                                                                                                                             |          |  |

|                                                                                                                               |    | 0x7 = Data Packet with a Timestamp                                                                                                                                                                                                                                                                                                                |          |  |

| NumMData 5                                                                                                                    |    | The number of metadata words in this packet. Each metadata word is CHDR_W bits wide. If NumMData is zero, then the packet has no metadata. The maximum value for NumMData is 30.  NOTE: Metadata is considered to be an advanced feature of RFNoC, and its interpretation is assumed to be block-specific. The framework will provide the ability |          |  |

|                                                                                                                               |    | for the user logic to extract and insert metadata into a packet but the user logic in the block is responsible for defining its format.                                                                                                                                                                                                           |          |  |

| SeqNum 16                                                                                                                     |    | Packet sequence number. The value shall start at 0 and increment by 1 for every packet of a given type in a stream. The counter shall roll over to 0 after 65535 (2 <sup>16</sup> -1).  NOTE: The sequence number is useful for detecting gaps and reordering issues in a stream. During error-                                                   |          |  |

|                                                                                                                               |    | free operation, the sequence number will increase monotonically (by 1) for every packet for each:                                                                                                                                                                                                                                                 |          |  |

|                                                                                                                               |    | <ul> <li>Stream (unique source and dest. endpoints)</li> <li>Packet type¹</li> </ul>                                                                                                                                                                                                                                                              |          |  |

|                                                                                                                               |    | The sequence should thus be independently monotonic for each stream and each packet type. A gap in the sequence number at any point is considered a sequence error.                                                                                                                                                                               |          |  |

| Length                                                                                                                        | 16 | Length of the packet in bytes. This includes the header, timestamp, metadata and payload.                                                                                                                                                                                                                                                         |          |  |

| DstEPID  The Endpoint ID of the stream endpoint that this packet is destined for. The EPID is used to make routing decisions. |    | Required                                                                                                                                                                                                                                                                                                                                          |          |  |

|                                                                                                                               |    | (The details of routing are covered in the following sections)  NOTE: EPID = 0 is reserved and may not be used                                                                                                                                                                                                                                    |          |  |

| Timestamp                                                                                                                     | 64 | A 64-bit integer timestamp for the payload in the packet.<br>This field is valid only when the packet type is "Data                                                                                                                                                                                                                               | Optional |  |

<sup>1</sup> Data packets with and without timestamps are considered the same type with respect to the sequence number.

|          |          | Packet with a Timestamp"                                                                                                                              |          |

|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Metadata | Variable | User-defined metadata. These bits are unused by the core framework and their format is undefined. The definition of the format can be block-specific. | Optional |

| Payload  | Variable | User-defined payload  NOTE: Every CHDR packet must have at least one line of payload.                                                                 | Required |

Table 2: CHDR field descriptions

The memory layout for various CHDR widths and configurations is shown below.

| Byte         | CHDR_W = 64 |  |

|--------------|-------------|--|

| 0            | HEADER (64) |  |

| 8            | METADATA[0] |  |

| 16           | METADATA[1] |  |

| 24           | PAYLOAD[0]  |  |

| 32           | PAYLOAD[1]  |  |

|              |             |  |

| PAYLOAD[N-1] |             |  |

Table 3: Memory layout for CHDR\_W = 64 (Example without a timestamp and 2 metadata words)

| Byte | CHDR_W = 64    |  |  |  |

|------|----------------|--|--|--|

| 0    | HEADER (64)    |  |  |  |

| 8    | TIMESTAMP (64) |  |  |  |

| 16   | METADATA[0]    |  |  |  |

| 24   | METADATA[1]    |  |  |  |

| 32   | PAYLOAD[0]     |  |  |  |

| 40   | PAYLOAD[1]     |  |  |  |

|      |                |  |  |  |

|      | PAYLOAD[N-1]   |  |  |  |

Table 4: Memory layout for CHDR\_W = 64 (Example with a timestamp and 2 metadata words)

| Byte | CHDR_W = 128               |  |  |  |  |

|------|----------------------------|--|--|--|--|

| 0    | TIMESTAMP (64) HEADER (64) |  |  |  |  |

| 16   | METADATA[0]                |  |  |  |  |

| 32   | METADATA[1]                |  |  |  |  |

| 48   | PAYLOAD[0]                 |  |  |  |  |

| 64   | PAYLOAD[1]                 |  |  |  |  |

|      |                            |  |  |  |  |

|      | PAYLOAD[N-1]               |  |  |  |  |

Table 5: Memory layout for CHDR W = 128 (Example with a timestamp and 2 metadata words)

| Byte | CHDR_W = 256 or higher              |  |  |  |  |

|------|-------------------------------------|--|--|--|--|

| 0    | RESERVED TIMESTAMP (64) HEADER (64) |  |  |  |  |

| 32   | METADATA[0]                         |  |  |  |  |

| 64   | METADATA[1]                         |  |  |  |  |

| 96   | PAYLOAD[0]                          |  |  |  |  |

| 128  | PAYLOAD[1]                          |  |  |  |  |

|      |                                     |  |  |  |  |

|      | PAYLOAD[N-1]                        |  |  |  |  |

Table 6: Memory layout for CHDR\_W = 256 (Example with a timestamp and 2 metadata words)

The amount of metadata in a packet depends on the NumMData field and the width of the CHDR bus. For compatibility between different CHDR widths, it is recommended to limit the amount of metadata to 248 bytes, the maximum amount supported by the smallest CHDR width, CHDR\_W = 64.

### 2.2.2 Data Packets

When the CHDR PktType field is 0x6 or 0x7, the payload is interpreted as a data packet. The data packet is the simplest type of CHDR packet because the format is flexible, and the payload is defined by the blocks generating and consuming it. When the PktType is 0x7, the header contains a valid timestamp. When the PktType is 0x6, the timestamp word is ignored. Note that when the PktType is 0x6 and CHDR\_W is 64, there is no timestamp word and the first word of metadata or payload immediately follows the header word.

The stream endpoints separate control traffic from data traffic so that the AXIS-CHDR Data ports on the client side of the stream endpoint only carry data packets (see Figure 1). Data packets are designed to have the lowest overhead to enable low-latency and high-throughput streaming of samples.

### 2.2.2.1 Timestamps and Data Bursts

The exact meaning of the timestamp field in data packets is a block-dependent feature. For example, the radio will add the current timestamp to each outgoing packet but will interpret the timestamp on incoming packets as an instruction to start sending at this time. Other blocks may also have block-specific behavior regarding timestamps. To harmonize the usage of timestamps, the following conventions should be used, where possible, to design blocks and/or software that uses timestamps:

- A burst is understood to be a contiguous string of samples or other data units. For example, the software might request 10000 samples from a radio, at a packet size of 1000 samples per packet. The burst will thus consist of 10 packets of 1000 samples each.

- The last packet of a burst must be tagged with an end-of-burst (EOB) marker.

- Assuming the burst is carrying timestamps, the first packet of the burst must carry the timestamp (the PktType field must be set to 0x7, and the 64-bit timestamp must be filled).

- The following packets of the burst *are not required* to carry a timestamp. The assumption is that timestamps can be calculated in the receiver, since the number of samples is known per packet.

- If mid-burst timestamps are set, then it is up to the downstream consumer to make use of them or ignore them.

- Example: The DDC block will calculate timestamps internally within a burst. This is because the DDC typically comes directly after a radio, and thus the input to the DDC is predictable. The RX Streamer (in software) however does read all incoming timestamps and passes them on the user. This is because the data link between the FPGA and the host computer can be lossy (e.g., when using UDP), and thus, the host software will not assume it can internally calculate new timestamps.

- The first packet after an EOB must carry a timestamp again, if the new burst is timed.

The rationale for not requiring timestamps mid-burst is twofold: First, timestamps mid-burst are redundant, and thus leaving them out might make block designs simpler, and potentially reduce bandwidth usage. The second reason is due to the fixed-point nature of timestamps. Take the example of a radio block producing data at a rate of 200 Msps, which is in the same clock domain as the timekeeper, running at 200 MHz. Following the radio block is a fractional resampler which turns the 200 Msps into a 122.88 Msps stream. Due to the fractional relationship between input and output rates at the resampler, it will not be able to calculate midburst timestamps without rounding errors. The timestamp in the first packet, however, does not need to be converted, since the beginning of the packet keeps the same time regardless of the sampling rate. The redundancy of the mid-burst timestamps is thus used to avoid potential pitfalls of fixed-point rounding errors.

### 2.2.3 Control Packets

When the CHDR PktType field is 0x4, the payload is interpreted as a control packet. The control packet encodes memory-mapped transactions. It has a variable length that can range from 16 bytes (no timestamp and NumData = 1) to 80 bytes (timestamp and NumData = 15).

Table 7 shows the format of the CHDR payload of a control packet. For simplicity, the rest of the CHDR packet is not shown. Note that a timestamp may be present in both the CHDR packet header and in the control packet contents. This simplifies the parsing of control and data packets.

| #   | Memory Layout < 64-bits> |         |       |         |          |          |            |         | Required<br>? |

|-----|--------------------------|---------|-------|---------|----------|----------|------------|---------|---------------|

| 0   | Reserved                 | SrcEPID | IsACK | HasTime | SeqNum   | NumData  |            | DstPort | Υ             |

|     | (16)                     | (16)    | (1)   | (1)     | (6)      | (4)      | (10)       | (10)    |               |

| 1   | Timestamp (64)           |         |       |         |          |          |            | N       |               |

| 2   | Data[0] Status           |         |       |         | Reserved | OpCode   | ByteEnable | Address | Υ             |

|     |                          | (2)     | (2)   | (4)     | (4)      | (20)     |            |         |               |

| 3   |                          | Data[   | [2]   |         |          | Da       | nta[1]     |         | N             |

|     |                          | (32     | )     |         |          |          | (32)       |         |               |

| ••• |                          |         |       |         |          |          |            | N       |               |

| 9   |                          | Data[   | 14]   | •       |          | Data[13] |            |         | N             |

|     |                          | (32     | )     |         |          |          | (32)       |         |               |

Table 7: Memory layout of the CHDR payload of a control packet

A detailed description of the fields is listed in Table 8. Each control packet has the source and destination stream endpoint. The packet also has a source and destination port which allows addressing up to 1024 NoC blocks from each endpoint.

| Field   | Width | Description                                                                                                                                                                                                            | Туре     |

|---------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| SrcEPID | 16    | The ID of the stream endpoint that this packet is originated from.  Note: EPID = 0 is reserved                                                                                                                         | Required |

| IsACK   | 1     | Is this an acknowledgement of a transaction completion?                                                                                                                                                                | Required |

| HasTime | 1     | A bit that indicates if the control transaction has the timestamp field                                                                                                                                                | Required |

| SeqNum  | 6     | Packet sequence number. For each master, the value shall start at 0, increment by 1 and roll over to 0 after 63 (2 <sup>6</sup> -1). This control-specific sequence number is independent of the CHDR sequence number. | Required |

|         |       | NOTE: The sequence number may not be sequential over the wire in a multi-master case. It will be sequential in the masters' ingress queue because the slave and the transport modules will                             |          |

|            |          | not modi                                                                    | fy it.                                                                                                           |          |

|------------|----------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------|

| NumData    | 4        | Number                                                                      | of 32-bit lines in the Data field                                                                                | Required |

|            |          | Note: Nu                                                                    | mData = 0 is reserved                                                                                            |          |

| SrcPort    | 10       |                                                                             | within the source stream endpoint that saction originated from.                                                  | Required |

| DstPort    | 10       |                                                                             | within the stream endpoint that this on needs to go to                                                           | Required |

| Timestamp  | 64       | the start                                                                   | nsaction is timed, then this field signifies time of the transaction. The Timestamp oot present if HasTime is 0. | Optional |

| Status     | 2        | When IsACK is high, this field indicates the transaction completion status: |                                                                                                                  | Required |

|            |          | Value                                                                       | Status                                                                                                           |          |

|            |          | 0x0                                                                         | OKAY (Transaction successful)                                                                                    |          |

|            |          | 0x1                                                                         | CMDERR (Slave asserted a command error)                                                                          |          |

|            |          | 0x2                                                                         | TSERR (Slave asserted a timestamp error)                                                                         |          |

|            |          | 0x3                                                                         | WARNING (Slave asserted a non-critical error)                                                                    |          |

| OpCode     | 4        |                                                                             | ration code of this transaction. See definitions below.                                                          | Required |

| ByteEnable | 4        | A bitmas                                                                    | k of the bytes to keep from the Data field                                                                       | Required |

| Address    | 20       | The byte                                                                    | address for the transaction                                                                                      | Required |

| Data[i]    | Variable | depends                                                                     | saction data. Number of data values<br>on the NumData field and their<br>ation depends on the OpCode.            | Optional |

Table 8: CHDR Control field definitions

A control transaction is a memory mapped transaction that contains a 20-bit Address field and a 4-bit byte-enable field (with behavior similar to tkeep/tstrb in AXI4). It may have one to fifteen 32-bit data fields. A transaction can be timed, i.e., only executed when the sample timestamp matches a command timestamp. The OpCode determines the behavior of the transaction. All register transactions must be acknowledged after they are consumed. The packet size of the response will be the same as the packet size of the request. Using this information, the sender is responsible for flow controlling control transactions to ensure that the control packet FIFO is not overrun.

Note that the use of some control transaction features is block-dependent. For example, some NoC blocks may ignore ByteEnable and/or the Timestamp if those blocks do not support those features. This allows NoC blocks to be simpler if such features are not required.

Table 9 shows the meaning of the OpCode field values.

| OpCode | Operation          | Arguments                              | Description                                                                                                                                                                                              |

|--------|--------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | Sleep              | [0]: Stall cycles                      | Do nothing and stall the control endpoint for<br>Data[0] clock cycles of the control interface<br>clock.                                                                                                 |

| 1      | Write              | [0]: Data                              | Write <i>Data</i> to a single register at <i>Address</i> at all bytes <i>p</i> where by <i>ByteEnable</i> [p] = 1.                                                                                       |

| 2      | Read               | [0]: Scratch                           | Read a single register at <i>Address</i> .                                                                                                                                                               |

| 3      | Read then<br>Write | [0]: Data                              | Read the register at <i>Address then</i> Write<br><i>Data</i> to it at all bytes <i>p</i> where by<br><i>ByteEnable</i> [p] = 1.                                                                         |

| 4      | Block Write        | [0]: Data[0] [N-1]: Data[N-1]          | Write Data[n] to registers sequentially at (Address + 4n) at all bytes p where by ByteEnable[p] = 1 where n = 0 N-1.                                                                                     |

| 5      | Block Read         | [0]: Scratch [0] [N-1]: Scratch [N-1]  | Read sequentially from registers at (Address + 4n) where n = 0 N-1.                                                                                                                                      |

| 6      | Poll               | [0]: Data<br>[1]: Mask<br>[2]: Timeout | Poll on Address until its value for all bits in Mask matches Data&Mask, or until Timeout cycles of control interface clock have elapsed. Acknowledge with CMDERR if timeout occurs, otherwise with OKAY. |

| 7-9    | Reserved           | Reserved                               | Reserved                                                                                                                                                                                                 |

| >9     | User Defined       | User Defined                           | 6 opcodes are reserved for user-specific implementation.                                                                                                                                                 |

Table 9: OpCode definitions for control transactions

### 2.2.3.1 AXI-Stream Control (AXIS-Ctrl) Interface

The CHDR Control packet is an example of a hierarchical packet format because the control payload itself forms another packet type, called AXIS-Ctrl, that is routed through the control infrastructure. AXIS-Ctrl is a 32-bit bus which is a serialized version of the payload of a CHDR Control packet. The stream endpoint will serialize CHDR to AXIS-Ctrl, where it is passed to the control crossbar. Each NoC Block will also receive and send control transactions/responses in

the AXIS-Ctrl format. The stream endpoint will then de-serialize these transactions back to CHDR.

**NOTE:** The AXIS-Ctrl data width is always 32 bits, regardless of the value of CHDR W.

### 2.2.4 Stream Status Packets [Internal Only]

NOTE: This is an internal-only packet, i.e., the NoC blocks will never see this type of packet. The RFNoC infrastructure is responsible for generating and consuming this packet type.

When the CHDR PktType field is 0x1, the payload is interpreted as a stream status packet. Data streams in RFNoC are always bidirectional. Stream status packets always flow in the opposite direction of a data packet stream to communicate stream health and flow control information.

The following is a 64-bit serialized representation of the stream status packet. For CHDR widths larger than 64, serialization/de-serialization to 64 bits is done least-significant word first.

| # | Memory Layout < 64-bits>   |          |  |          |         |   |

|---|----------------------------|----------|--|----------|---------|---|

| 0 | CapacityBytes              | Reserved |  | Status   | SrcEPID | Υ |

|   | (40)                       | (4)      |  | (4)      | (16)    |   |

| 1 | XferCountPkts CapacityPkts |          |  |          |         | Υ |

|   | (40                        | )        |  | (24)     |         |   |

| 2 | XferCountBytes             |          |  |          |         | Υ |

|   | (64)                       |          |  |          |         |   |

| 3 | StatusInfo                 |          |  | BuffInfo |         | Υ |

|   | (48)                       |          |  | (16      | )       |   |

Table 10: Memory layout of the CHDR payload of a stream status packet

| Field             | Width | Description                                             | Туре     |

|-------------------|-------|---------------------------------------------------------|----------|

| Capacity<br>Bytes | 40    | The buffer capacity of the downstream endpoint in bytes | Required |

| Status            | 4     | The current status of the stream. Possible values:      | Required |

|                   |       | 0x0 = Okay (No Error)                                   |          |

|                   |       | 0x1 = Command Error (Command execution failed)          |          |

|                   |       | 0x2 = Sequence Error (Sequence number discontinuity)    |          |

|                   |       | 0x3 = Data Error (Data integrity check failed)          |          |

|                   |       | 0x4 = Routing Error (Unexpected destination)            |          |

|                    |    | Others = Reserved                                                                                                                   |          |

|--------------------|----|-------------------------------------------------------------------------------------------------------------------------------------|----------|

| SrcEPID            | 16 | Endpoint ID of the source of this message  NOTE: The endpoint ID of the destination is present in the CHDR header                   | Required |

| XferCount<br>Pkts  | 40 | Number of packets received by the destination stream endpoint.                                                                      | Required |

| Capacity<br>Pkts   | 24 | The buffer capacity of the downstream endpoint in packets                                                                           | Required |

| XferCount<br>Bytes | 64 | Number of bytes received by the destination stream endpoint.                                                                        | Required |

| StatusInfo         | 48 | Extended information about the status.  NOTE: The format of this field is unspecified. It shall be used for diagnostics only.       | Required |

| BuffInfo           | 16 | Extended information about the buffer state.  NOTE: The format of this field is unspecified. It shall be used for diagnostics only. | Required |

Table 11: Stream status packet field definitions

### 2.2.5 Stream Command Packets [Internal Only]

NOTE: This is an internal-only packet, i.e., the NoC blocks will never see this type of packet. The RFNoC infrastructure is responsible for generating and consuming this packet type.

When the CHDR PktType field is 0x2, the payload is interpreted as a stream command. Data streams in RFNoC are always bidirectional. Stream command packets always flow in the direction of a data packet stream to trigger stream state changes.

The following is a 64-bit serialized representation of the stream status packet. For CHDR widths larger than 64, serialization/de-serialization to 64 bits is done least-significant word first.

| # | Memory Layout <> |               |               |                 |   |  |

|---|------------------|---------------|---------------|-----------------|---|--|

| 0 | NumPkts<br>(40)  | OpData<br>(4) | OpCode<br>(4) | SrcEPID<br>(16) | Y |  |

| 1 | NumBytes<br>(64) |               |               |                 |   |  |

Table 12: Memory layout of the CHDR payload of a stream command packet

| Field    | Width | Description                                                        | Description                                                                                                                                                                                                                                                                                                                                                                              |          |  |  |  |  |  |  |  |  |     |                                     |  |

|----------|-------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|--|--|-----|-------------------------------------|--|

| NumPkts  | 40    |                                                                    | The number of packets associated with the operation. The exact interpretation of this field depends on the OpCode.                                                                                                                                                                                                                                                                       |          |  |  |  |  |  |  |  |  |     |                                     |  |

| OpData   | 4     |                                                                    | associated with the operation. The exact ion of this field depends on the OpCode.                                                                                                                                                                                                                                                                                                        | Required |  |  |  |  |  |  |  |  |     |                                     |  |

| OpCode   | 4     | A code tha                                                         | at describes what needs to be done.                                                                                                                                                                                                                                                                                                                                                      | Required |  |  |  |  |  |  |  |  |     |                                     |  |

|          |       | Value                                                              | Operation                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |  |  |  |     |                                     |  |

|          |       | 0x0                                                                | Initialize stream Flush buffers and reset stream state.                                                                                                                                                                                                                                                                                                                                  |          |  |  |  |  |  |  |  |  |     |                                     |  |

|          |       |                                                                    | NOTE: When an Initialize stream command packet with NumBytes==0 and NumPkts==0 is received by the RFNoC infrastructure, one and only one stream status packet shall be sent in response. No flow control stream status packets shall be sent in response to incoming data on the given stream until an Initialize stream command packet with either NumBytes>0 or NumPkts>0 is received. |          |  |  |  |  |  |  |  |  |     |                                     |  |

|          |       | <ul><li>endpoint.</li><li>0x2 Resynchro</li><li>Use NumF</li></ul> |                                                                                                                                                                                                                                                                                                                                                                                          |          |  |  |  |  |  |  |  |  | 0x1 | Trigger a stream status response at |  |

|          |       |                                                                    | Resynchronize flow control  Use NumPkts and NumBytes to resync flow control.                                                                                                                                                                                                                                                                                                             |          |  |  |  |  |  |  |  |  |     |                                     |  |

|          |       | Others                                                             | Reserved                                                                                                                                                                                                                                                                                                                                                                                 |          |  |  |  |  |  |  |  |  |     |                                     |  |

| SrcEPID  | 16    | NOTE: Th                                                           | Endpoint ID of the source of this message.  NOTE: The endpoint ID of the destination is present in the CHDR header                                                                                                                                                                                                                                                                       |          |  |  |  |  |  |  |  |  |     |                                     |  |

| NumBytes | 64    | The numb The exact OpCode.                                         | Required                                                                                                                                                                                                                                                                                                                                                                                 |          |  |  |  |  |  |  |  |  |     |                                     |  |

Table 13: Stream command packet field definitions

### 2.2.6 Management Packets [Internal Only]

NOTE: This is an internal-only packet, i.e., the NoC blocks will never see this type of packet. The RFNoC infrastructure is responsible for generating and consuming this packet type.

When the CHDR PktType field is 0x0, the payload is interpreted as a management packet. Management packets are sent and received by internal RFNoC framework components for discovery and internal configuration. The following information can be discovered:

- The RFNoC protocol version and capabilities

- The physical connection topology including all transport endpoints and routers

A management packet can configure and discover information on the various nodes in the network. Nodes can be transport endpoints, crossbars and stream endpoints. The packet is a multi-hop transaction where operations are encoded in layers that are "peeled off" as they are consumed by the various nodes. A hop may contain several operations to execute (with a minimum of one). Each operation has an 8-bit opcode and a 48-bit payload. The interpretation of the payload is operation specific. The various opcodes defined below can allow the following:

- Discovering the RFNoC connection topology one node at a time (in DFS or a BFS manner)

- Configuring transport endpoints to setup EPID-specific settings

- Configuring stream endpoints with flow-control and other settings

Configuration is done via a basic memory mapped writes with a 16-bit address and 32-bit data. In the case of a route setup, the management packet can be configured to terminate at the stream endpoint. For other situations, it can be configured to return to the host.

The following is a 64-bit serialized representation of a management packet. For CHDR widths larger than 64, only the lower 64 bits of each management packet word are used and the upper bits will be ignored. Management packets are NOT serialized.

| #   | Memory Layout < 64-bits> |           |          |         |            |   |

|-----|--------------------------|-----------|----------|---------|------------|---|

| 0   | ProtoVer                 | CHDRWidth | Reserved | NumHops | SrcEPID    | Υ |

|     | (16)                     | (3)       | (19)     | (10)    | (16)       |   |

| 1   |                          | OpPaylo   | ad       | OpCode  | OpsPending | Υ |

|     |                          | (48)      |          | (8)     | (8)        |   |

| ••• |                          |           |          | •••     |            | N |

| N-1 |                          | OpPaylo   | ad       | OpCode  | OpsPending | N |

|     |                          | (48)      |          | (8)     | (8)        |   |

Table 14: Memory layout of the CHDR payload of a management packet

| Field | Width | Description | Туре |

|-------|-------|-------------|------|

|       |       |             |      |

| 5              | 1.0 | DEN 0 /                            |                                                                                                                                         |          |  |

|----------------|-----|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------|--|

| ProtoVer       | 16  | RFNoC protoc                       |                                                                                                                                         | Required |  |

|                |     | •                                  | represent the major version, and the epresent the minor version                                                                         |          |  |

| OLID DVA/S-IH- |     |                                    |                                                                                                                                         | Demined  |  |

| CHDRWidth      | 3   |                                    | bus width (CHDR_W)                                                                                                                      | Required |  |

|                |     | 0x0 = 64  bits                     |                                                                                                                                         |          |  |

|                |     | 0x1 = 128  bits<br>0x2 = 256  bits |                                                                                                                                         |          |  |

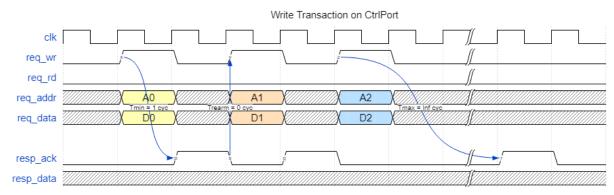

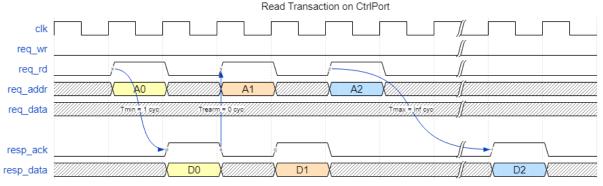

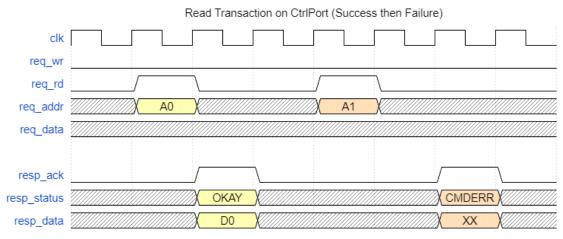

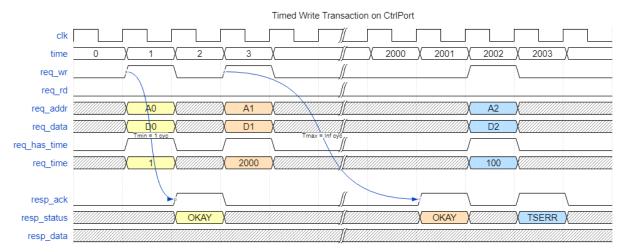

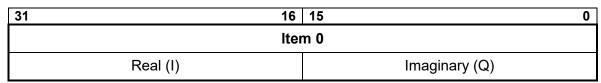

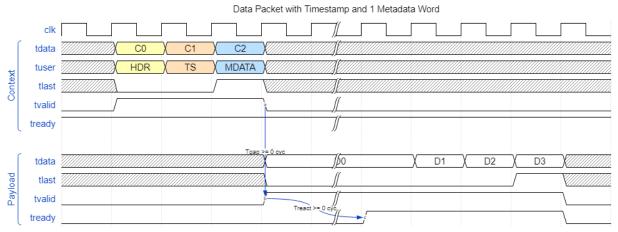

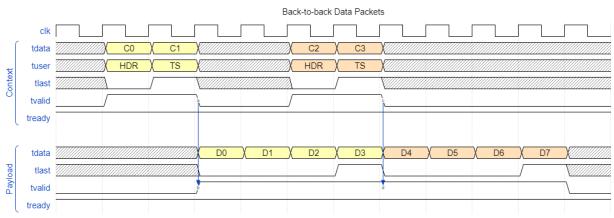

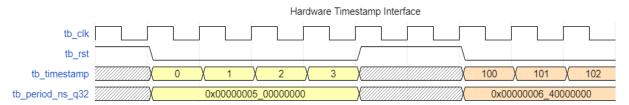

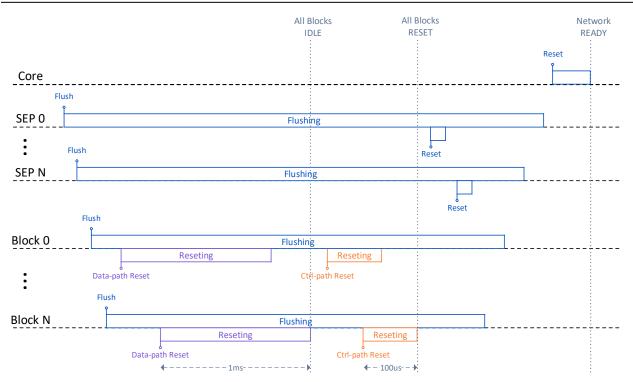

|                |     | 0x2 = 250  bits<br>0x3 = 512  bits |                                                                                                                                         |          |  |